—Starting Point

As a music lover, I thought that it would be a fun project because it combines analog and digital circuitry to create a relatively efficient speaker.

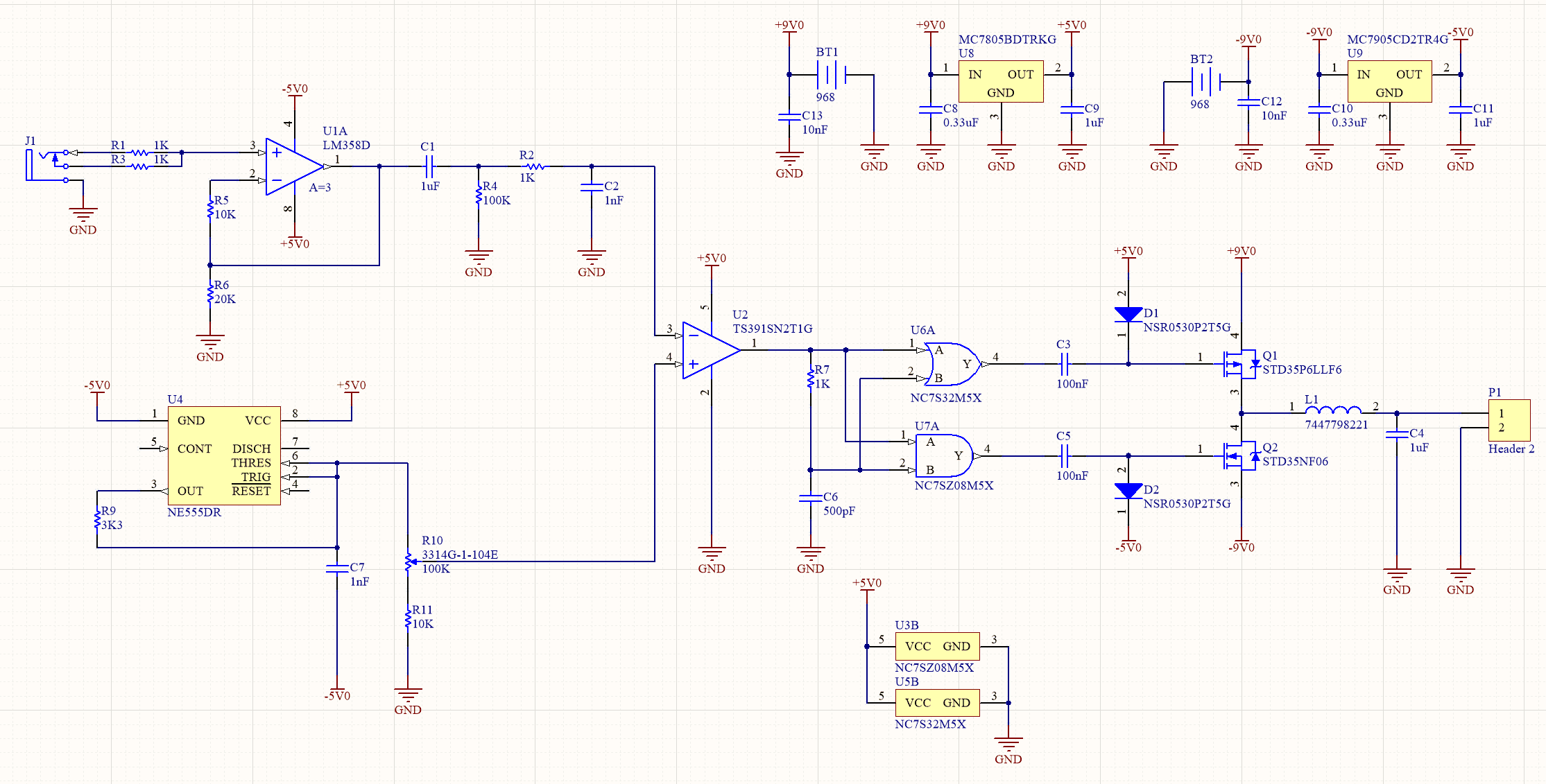

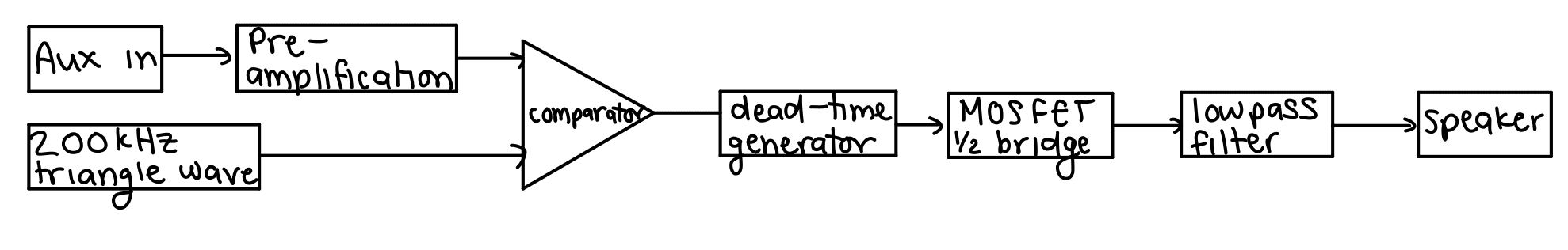

I started with a block diagram for a standard class-d amplifier:

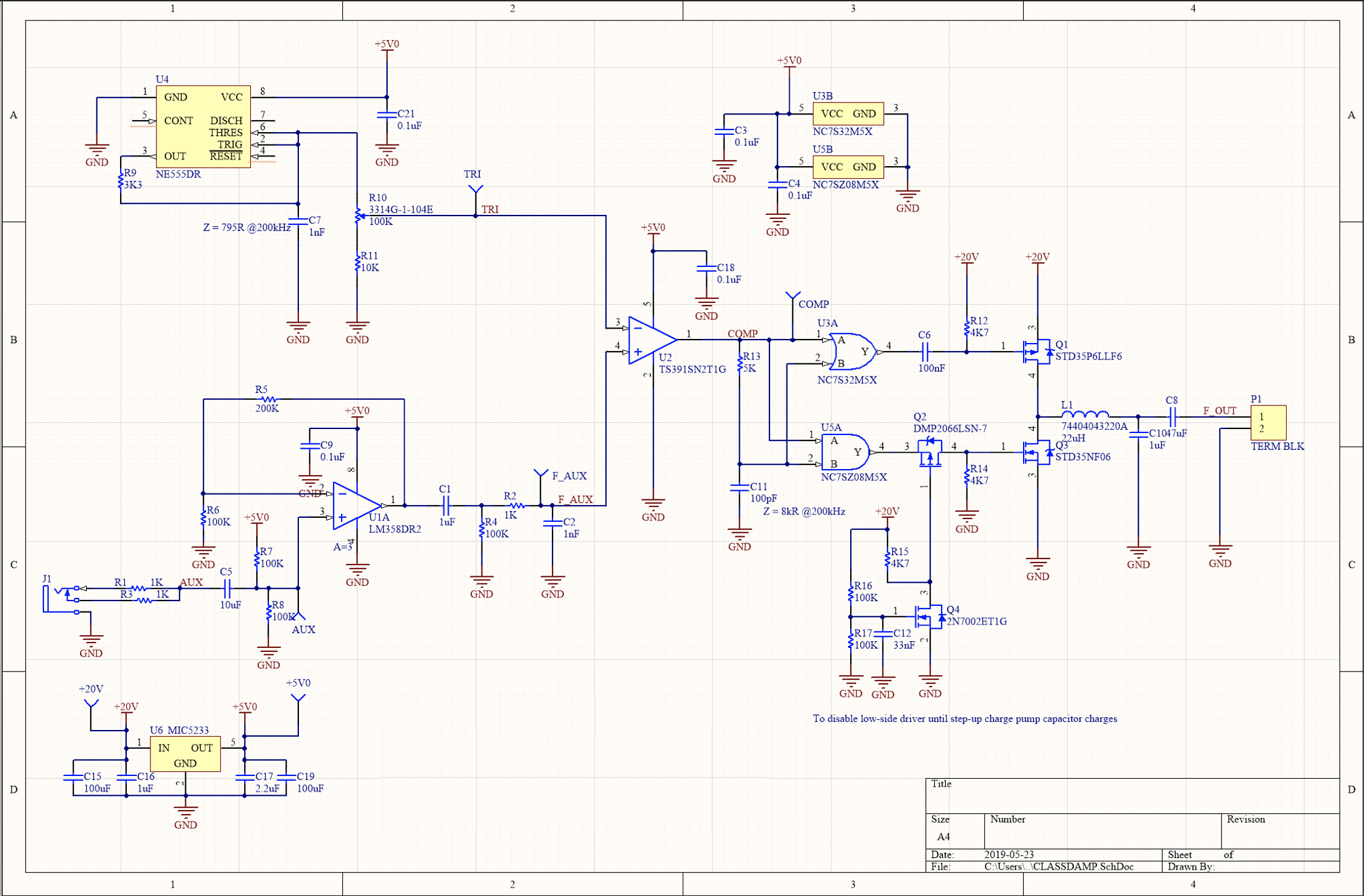

Some notes

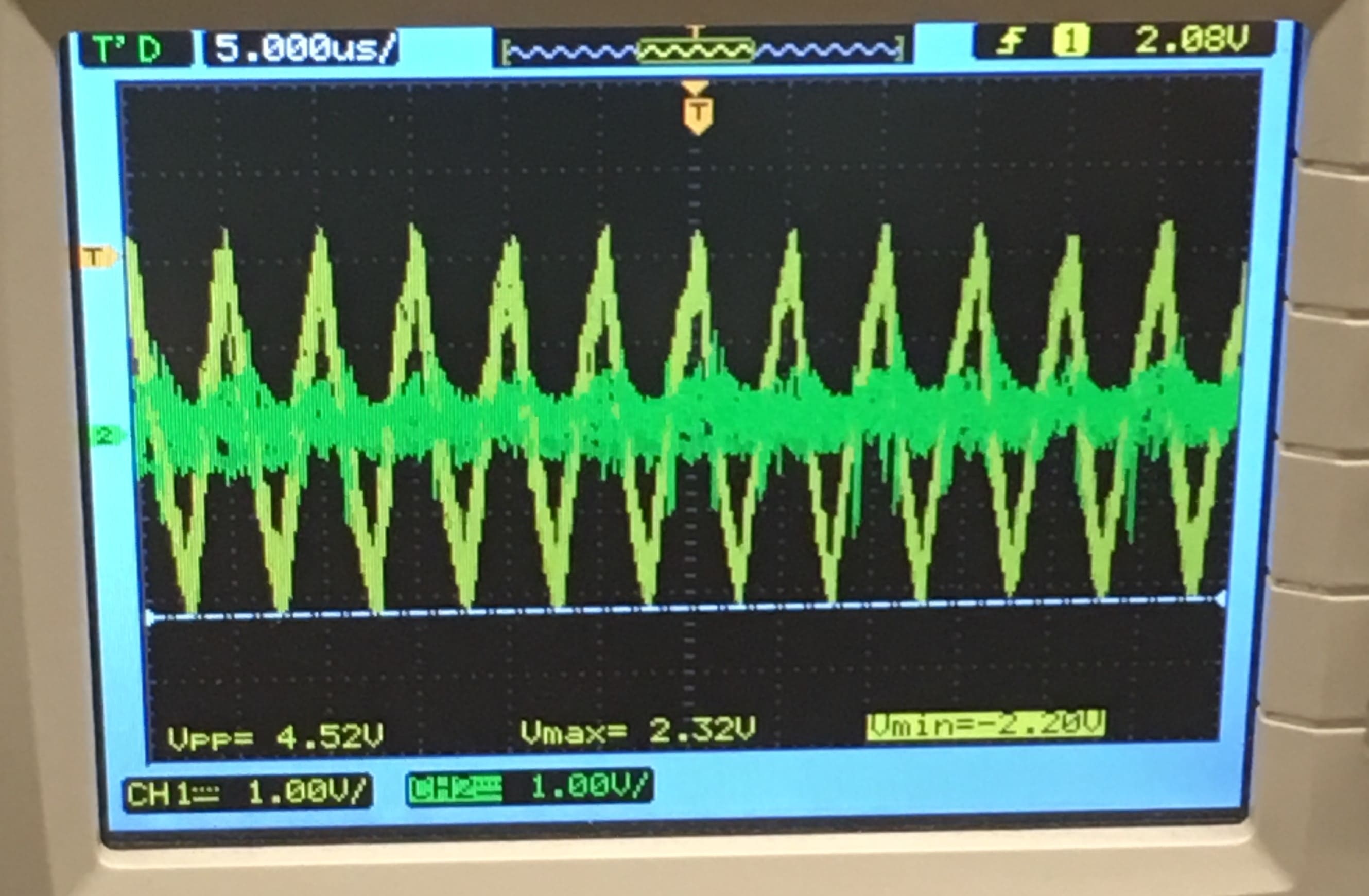

Aux in: The signal (when measured) was around 60mV.

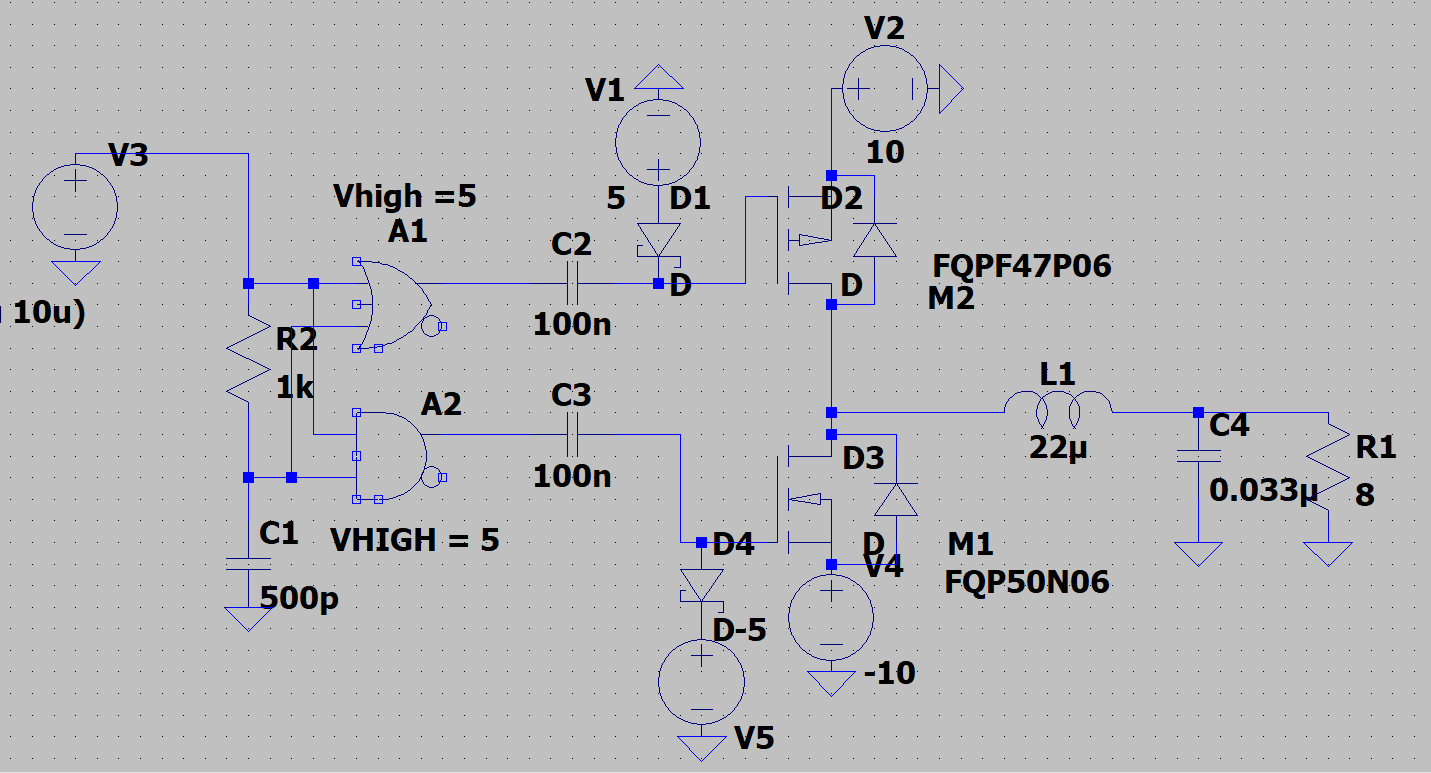

200kHz triangle wave: 200kHz is 10x the upper limit of human hearing, so the sound quality will be maintained when the audio signal is encoded as a time-varying PWM signal.

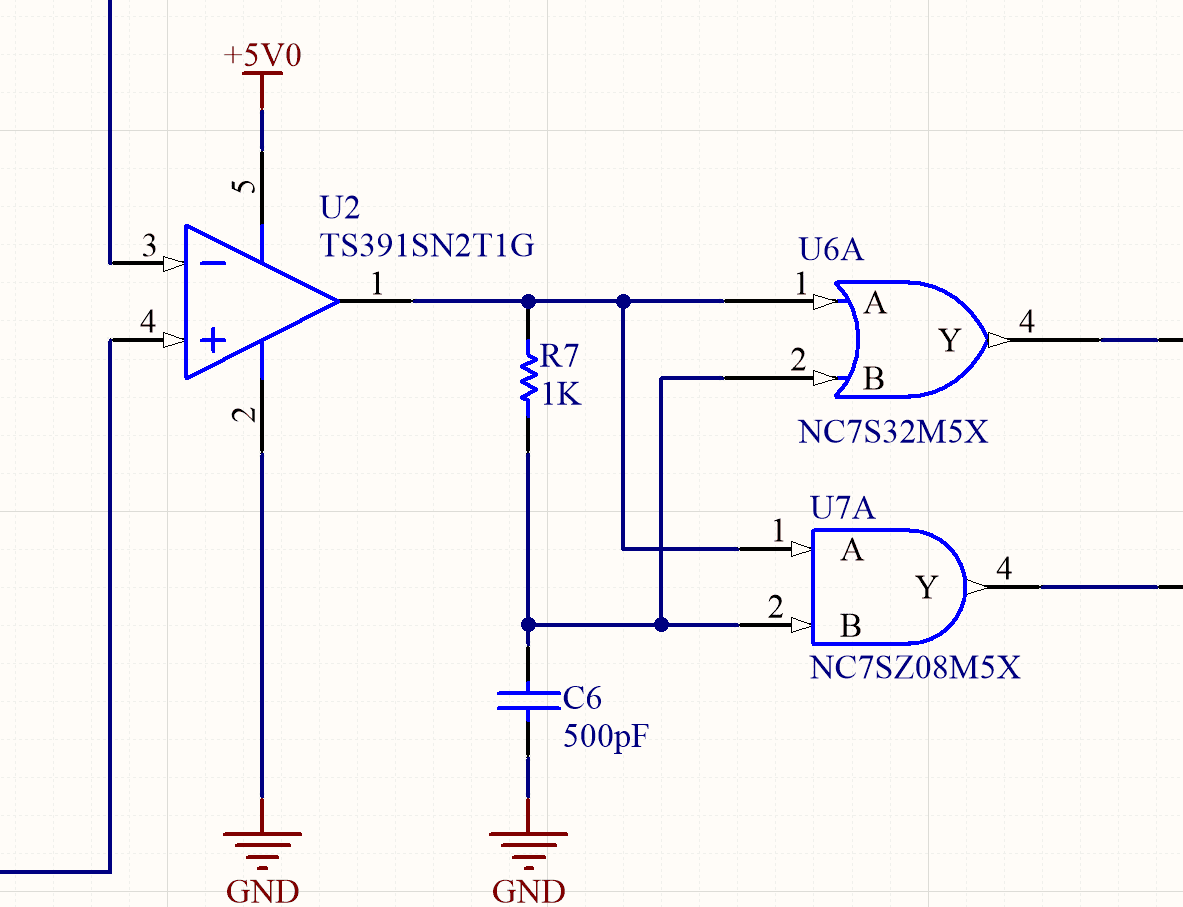

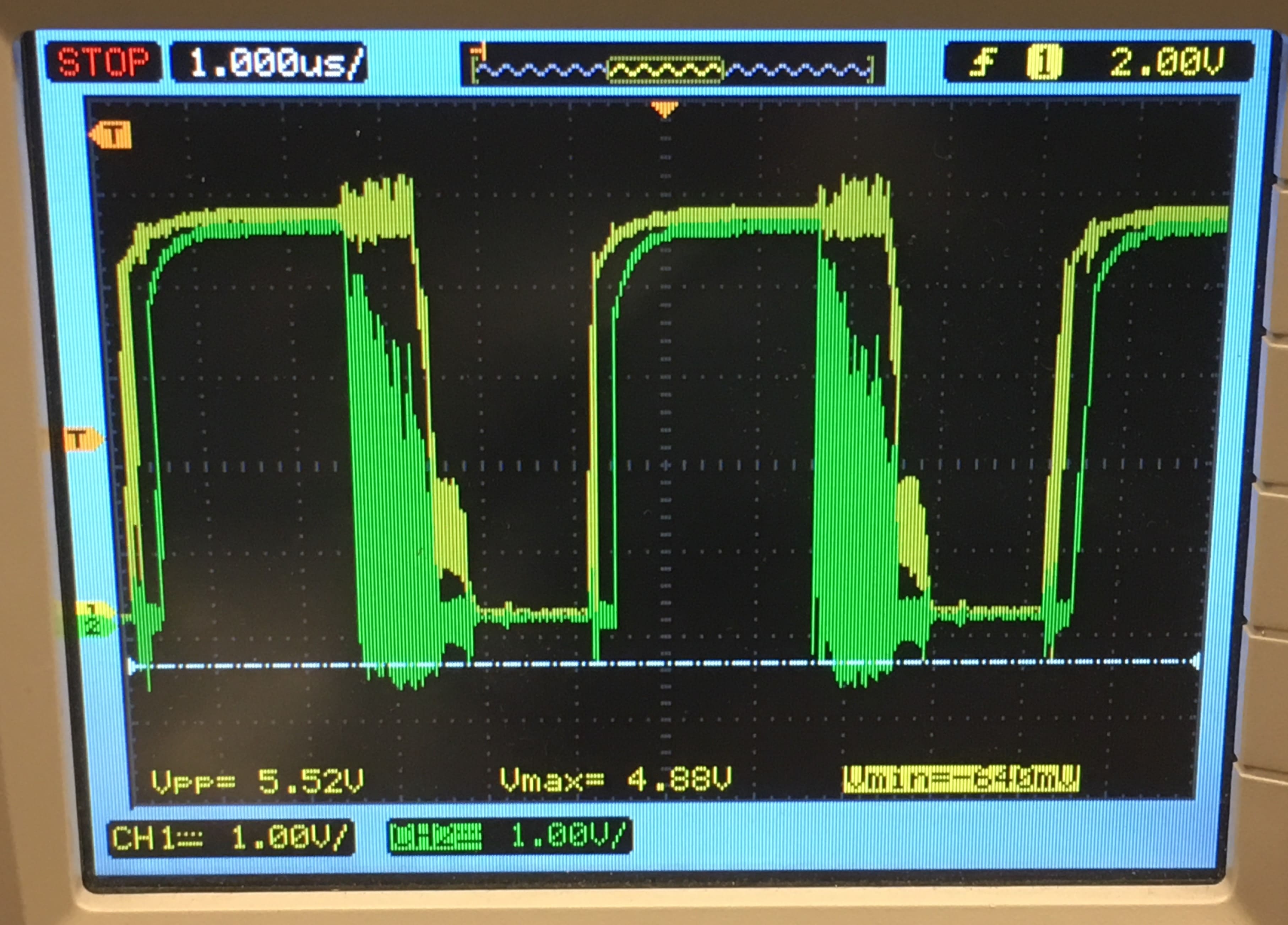

Comparator: Propagation delays of the selected component need to be much lower than 5us (the frequency of the triangle wave)

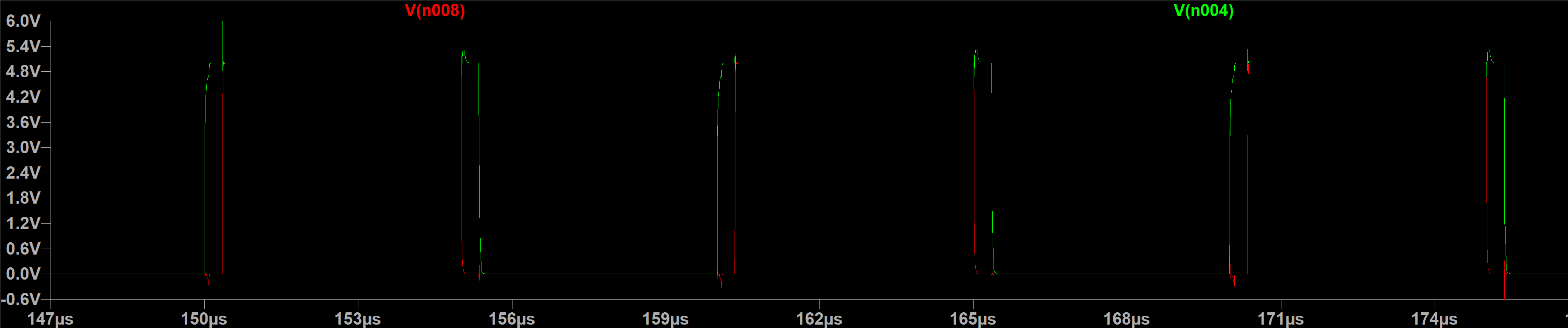

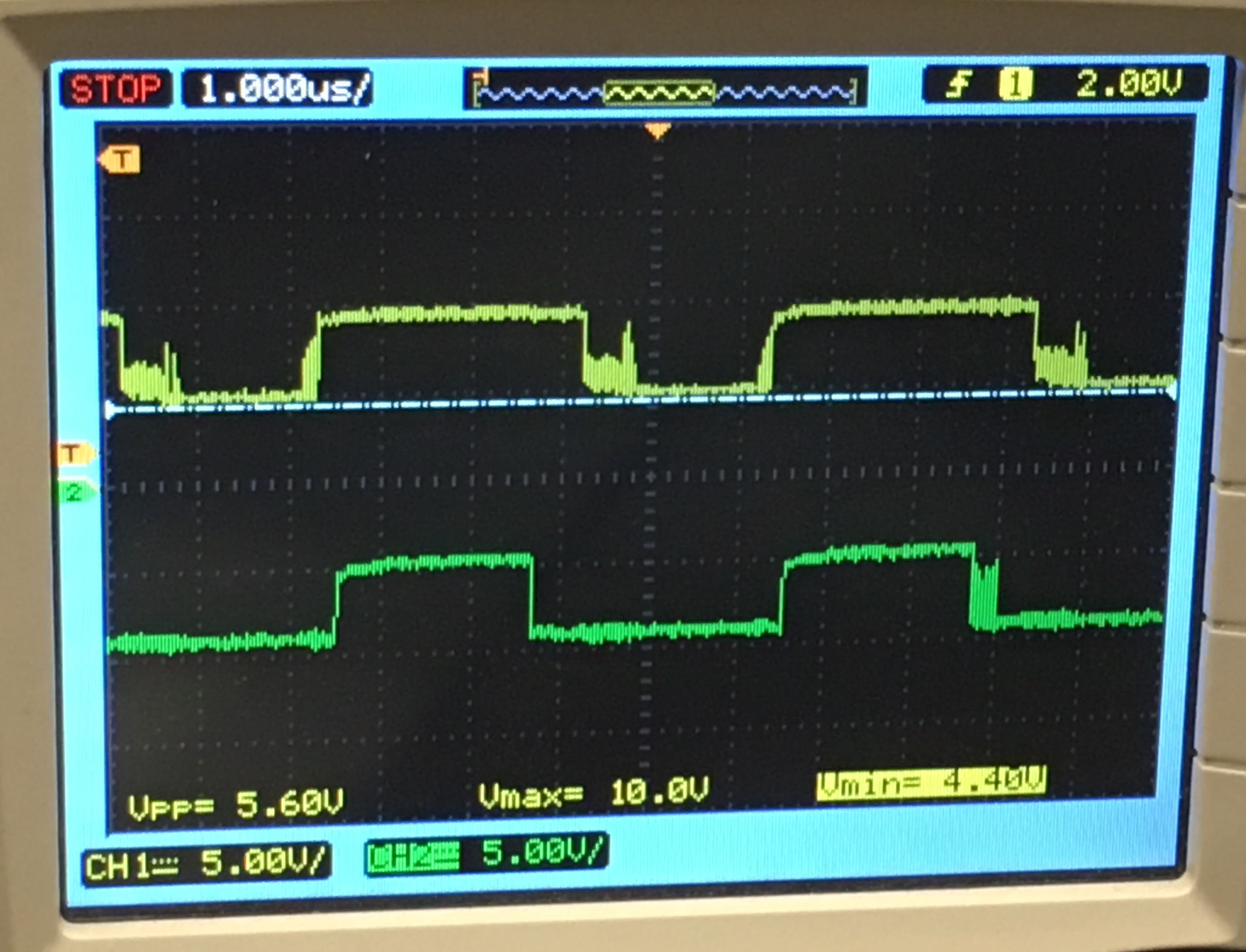

Dead-time generator: The high-side and low-side MOSFETs cannot be on at the same time.

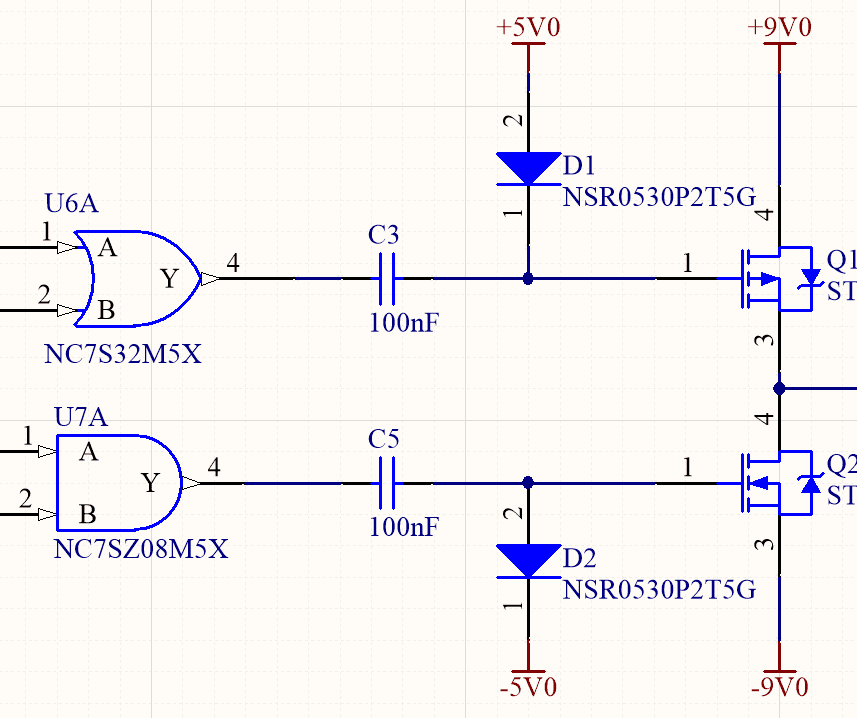

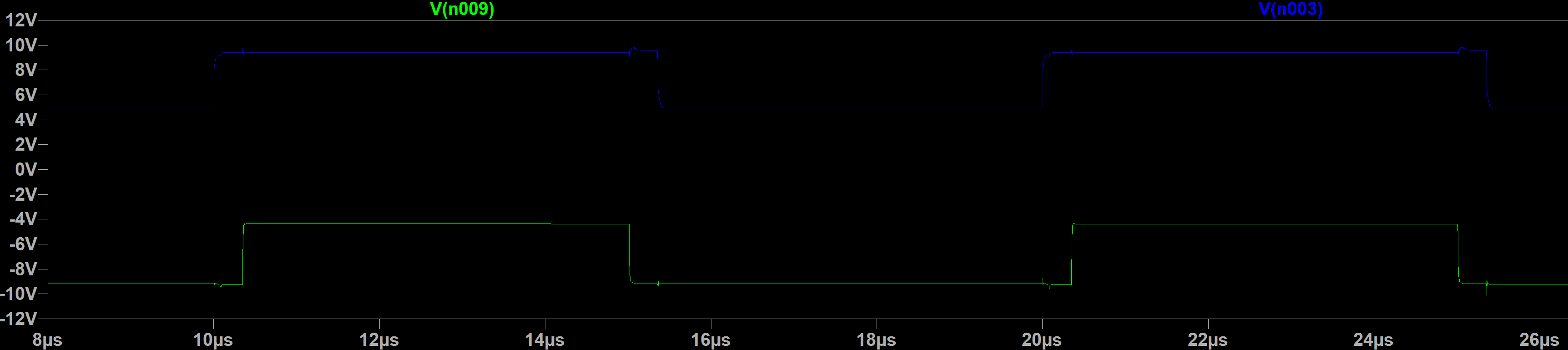

MOSFET 1/2 bridge: The selected switches should have similar switching characteristics.

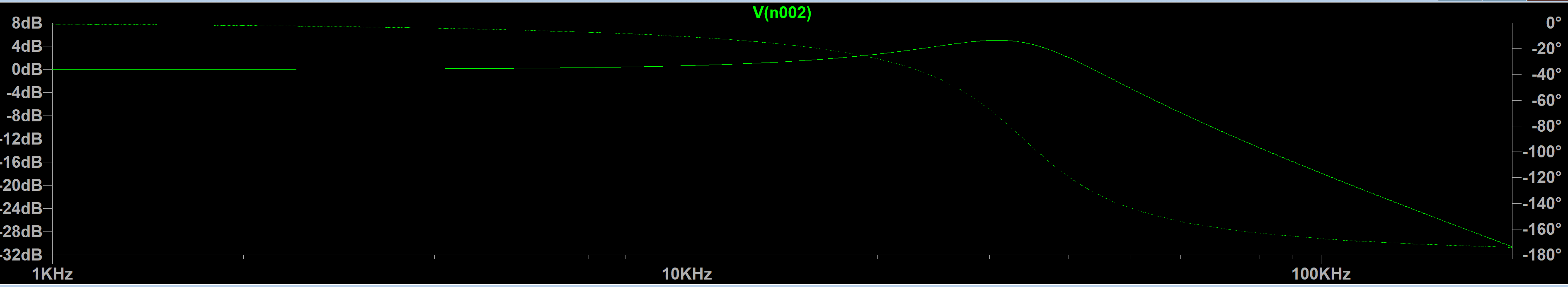

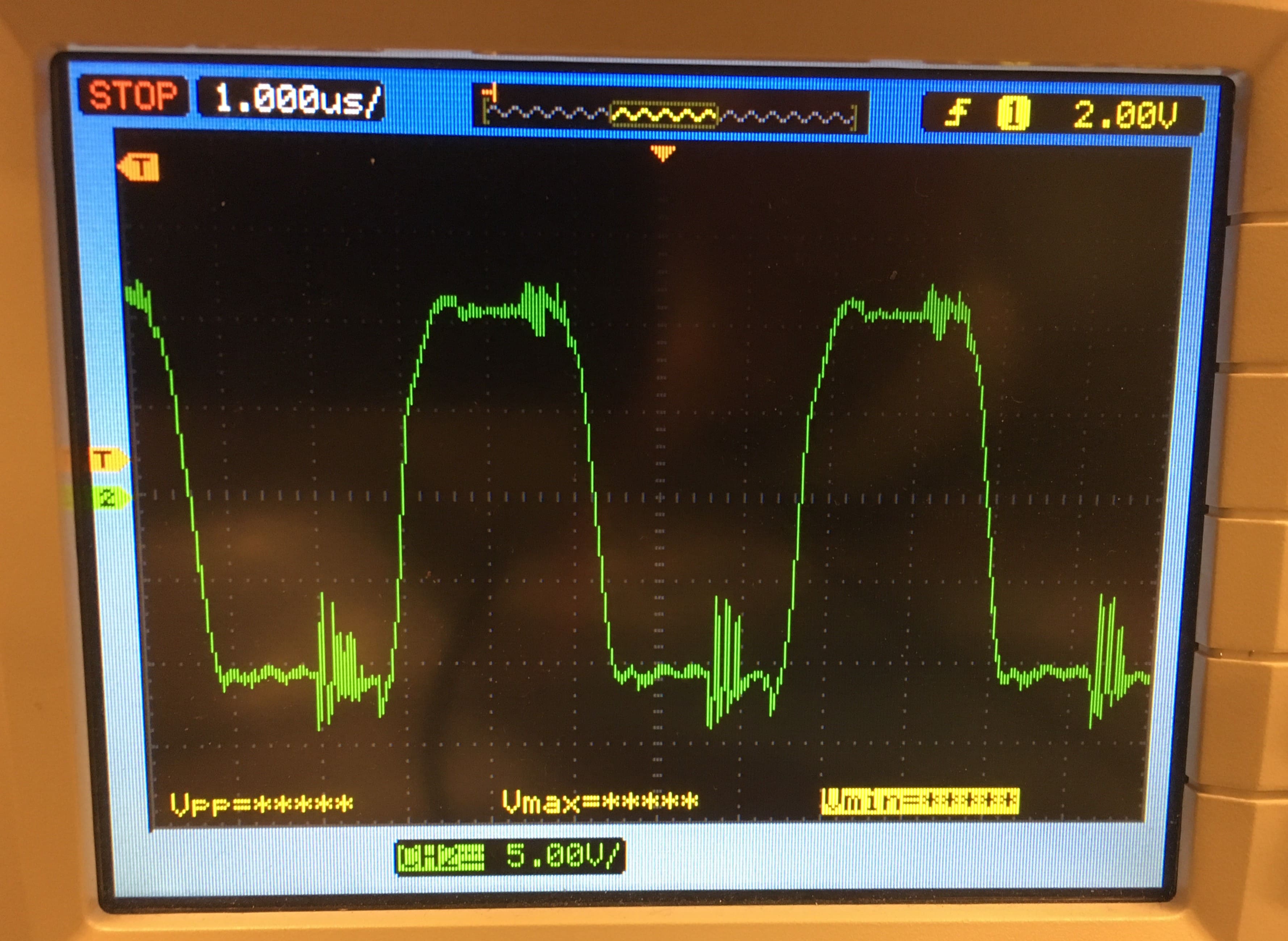

Low Pass Filter: Most class-D amplifiers utilize an LC filter, and the cut-off frequency should be around 30kHz.